DEVELOPMENT KIT BOARD USER MANUAL PMC-2001840

PM2352 FREEDM™-32P672

ISSUE 1

DEVELOPMENT KIT BOARD USER MANUAL

PM7380

## FREEDMTM-32P672

## **DEVELOPMENT KIT**

**USER MANUAL**

RELEASED ISSUE 1: DECEMBER 2000

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS' INTERNAL USE

DEVELOPMENT KIT BOARD USER MANUAL PMC-2001840 PMC-Sierra, Inc.

ISSUE 1

DEVELOPMENT KIT BOARD USER MANUAL

### **CONTENTS**

| 1 | OVERVIEW |                                                                     |

|---|----------|---------------------------------------------------------------------|

|   | 1.1      | FEATURES 1                                                          |

| 2 | HARE     | WARE CONFIGURATION 2                                                |

|   | 2.1      | VOLTAGE SELECTION                                                   |

|   | 2.2      | SYSCLK JUMPER SETTING 5                                             |

|   | 2.3      | JUMPER SETTING FOR RMVCK[3:0] PROVISION                             |

|   | 2.4      | JUMPER SETTING FOR TMVCK[3:0] PROVISION 6                           |

|   | 2.5      | JUMPER SETTINGS FOR TMV8DC, RMV8DC, TMV8FPC AND RMV8FPC PROVISION   |

|   | 2.6      | JUMPER SETTINGS FOR TFP8B AND RFP8B                                 |

|   | 2.7      | JUMPER SETTINGS FOR RFPB[3:0] 10                                    |

|   | 2.8      | JUMPER SETTINGS FOR TFPB[3:0]11                                     |

|   | 2.9      | JUMPER SETTINGS FOR SELECTION OF RCLK[2:0] AND TCLK[2:0]            |

|   | 2.10     | JUMPER SETTINGS FOR ENABLING OF RCLK[15:0] 13                       |

|   | 2.11     | JUMPER SETTINGS FOR ENABLING OF RCLK[31:16] 15                      |

|   | 2.12     | JUMPER SETTINGS FOR ENABLING OF TCLK[15:0] 17                       |

|   | 2.13     | JUMPER SETTINGS FOR ENABLING OF TCLK[31:16]18                       |

|   | 2.14     | JUMPER SETTINGS FOR DATA LOOPBACK ON LINKS 2<br>THROUGH 31          |

|   | 2.15     | JUMPER SETTINGS FOR DATA LOOPBACK/CROSS-CONNECT<br>ON LINKS 0 AND 1 |

|   | 2.16     | JUMPER SETTINGS FOR BERT EMULATION 22                               |

|   | 2.17     | PLACEMENT OF OSCILLATORS IN THE SOCKETS 23                          |

|   |          |                                                                     |

DEVELOPMENT KIT BOARD USER MANUAL PMC-2001840

DEVELOPMENT KIT BOARD USER MANUAL

PM2352 FREEDM™-32P672

3 3.1 3.2 CONFIGURATION FOR UNCHANNELIZED T1 LOOPBACK CONFIGURATION FOR UNCHANNELIZED E1 LOOPBACK 3.3 CONFIGURATION FOR 16 T1/ 16 E1 UNCHANNELIZED 3.4 3.5 CONFIGURATION FOR UNCHANNELIZED MIXED DS3/T1/E1 3.6 CONFIGURATION FOR UNCHANNELIZED 2.048 MBIT/S H-MVIP 3.7 CONFIGURATION FOR UNCHANNELIZED 8.192 MBIT/S H-MVIP 3.8 BERT SIGNAL VERIFICATION ...... 41 3.9 HOW TO PROCEED WITH THE TEST CASES ...... 44 4

PMC-Sierra, Inc.

ISSUE 1

PMC-Sierra, Inc.

DEVELOPMENT KIT BOARD USER MANUAL

### LIST OF FIGURES

| FIGURE 1 FREEDM <sup>TM</sup> -32P672 DEVELOPMENT KIT BOARD DIAGRAM 3              |

|------------------------------------------------------------------------------------|

| FIGURE 2 3.3V SELECTION HEADER (P16) 4                                             |

| FIGURE 3 LEDS ON THE FREEDM <sup>TM</sup> -32P672 DEVELOPMENT KIT                  |

| FIGURE 4 JUMPER SETTING FOR SYSCLK (P3) 5                                          |

| FIGURE 5 JUMPER SETTINGS FOR RMVCK[3:0] (P5) 6                                     |

| FIGURE 6 JUMPER SETTING FOR TMVCK[3:0] (P6)7                                       |

| FIGURE 7 JUMPER SETTINGS FOR ENABLING OF RMV8FPC, TMV8FPC, TMV8DC, AND RMV8DC (P4) |

| FIGURE 8 JUMPER SETTINGS FOR RFP8B AND TFP8B (P9) 9                                |

| FIGURE 9 JUMPER SETTINGS FOR RFPB[3:0] (P8) 10                                     |

| FIGURE 10JUMPER SETTINGS FOR TFPB[3:0] (P1)11                                      |

| FIGURE 11 JUMPER SETTINGS FOR SELECTION OF RCLK[2:0] AND TCLK[2:0] (P7)            |

| FIGURE 12JUMPER SETTINGS FOR ENABLING OF RCLK[15:0] (P12) 14                       |

| FIGURE 13JUMPER SETTINGS FOR ENABLING OF RCLK[31:16] (P11) 16                      |

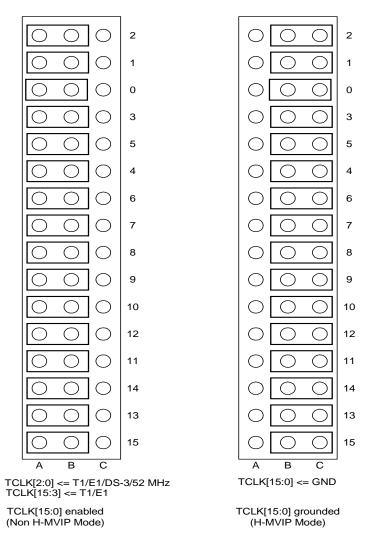

| FIGURE 14JUMPER SETTINGS FOR ENABLING OF TCLK[15:0] (P13) 17                       |

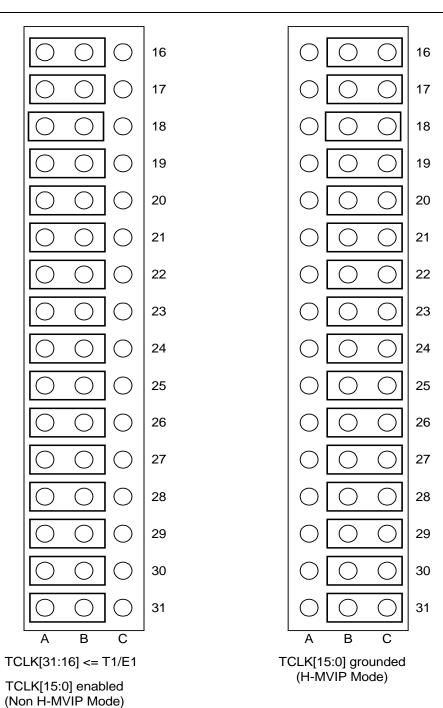

| FIGURE 15JUMPER SETTINGS FOR TCLK[31:16] (P14) 19                                  |

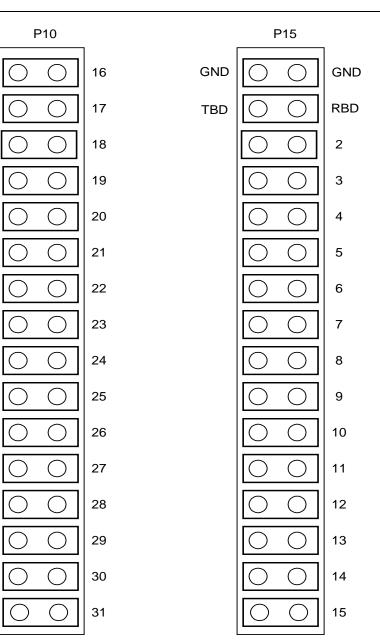

| FIGURE 16JUMPER SETTINGS FOR DATA LOOPBACK ON LINKS 2 TO 3121                      |

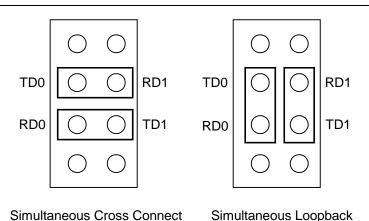

| FIGURE 17JUMPER SETTINGS FOR LOOPBACK/CROSS-CONNECT ON<br>LINKS 0 AND 1 (P2)       |

| FIGURE 18JUMPER SETTINGS FOR BERT DATA EMULATION (P15) 22                          |

| FIGURE 19JUMPER SETTINGS FOR BERT CLOCK EMULATION (P7) 23                          |

DEVELOPMENT KIT BOARD USER MANUAL PMC-2001840

ISSUE 1

PMC-Sierra, Inc.

DEVELOPMENT KIT BOARD USER MANUAL

### LIST OF TABLES

| TABLE 1              | JUMPER SETTING FOR SYSCLK                                    | . 5 |

|----------------------|--------------------------------------------------------------|-----|

| TABLE 2              | JUMPER SETTINGS FOR RMVCK[3:0]                               | . 6 |

| TABLE 3              | JUMPER SETTING FOR TMVCK[3:0]                                | . 7 |

| TABLE 4<br>TMV8DC, A | JUMPER SETTINGS FOR ENABLING OF RMV8FPC, TMV8FPC, AND RMV8DC |     |

| TABLE 5              | JUMPER SETTINGS FOR RFP8B AND TFP8B                          | . 9 |

| TABLE 6              | JUMPER SETTINGS FOR RFPB[3:0]                                | 11  |

| TABLE 7              | JUMPER SETTINGS FOR TFPB[3:0]                                | 11  |

| TABLE 8<br>TCLK[2:0] | JUMPER SETTINGS FOR SELECTION OF RCLK[2:0] AND               | 13  |

| TABLE 9              | JUMPER SETTINGS FOR ENABLING OF RCLK[15:0]                   | 14  |

| TABLE 10             | JUMPER SETTINGS FOR ENABLING OF RCLK[31:16]                  | 15  |

| TABLE 11             | JUMPER SETTINGS FOR TCLK[15:0]                               | 18  |

| TABLE 12             | JUMPER SETTINGS FOR ENABLING TCLK[31:16]                     | 18  |

|                      | JUMPER SETTINGS FOR DATA LOOPBACK ON LINKS 2                 | 20  |

|                      | JUMPER SETTINGS FOR LOOPBACK/CROSS-CONNECT ON<br>ND 1        | 22  |

| TABLE 15             | JUMPER SETTINGS FOR BERT CLOCK EMULATION                     | 23  |

| TABLE 16             | OSCILLATOR PLACEMENT IN SOCKETS                              | 23  |

| TABLE 17             | CONFIGURATION FOR THE PCI INTERFACE TEST                     | 25  |

|                      | CONFIGURATION FOR SIMULTANEOUS LOOPBACK OF E1 DA             |     |

| TABLE 19<br>31       | CONFIGURATION FOR 16 T1/E1 UNCHANNELIZED LOOPBACK            | <   |

DEVELOPMENT KIT BOARD USER MANUAL PMC-2001840

**ISSUE 1**

| TABLE 20SIMULTANEOUS LOOPBACK OF UNCHANNELIZED 52 MBIT/SDATA ON LINKS 0 THROUGH 233 |

|-------------------------------------------------------------------------------------|

| TABLE 21SIMULTANEOUS LOOPBACK OF UNCHANNELIZED MIXEDDS3/T1/E1DATA35                 |

| TABLE 22CONFIGURATION FOR UNCHANNELIZED 2.048 MBIT/S H-MVIPDATA LOOPBACK38          |

| TABLE 23CONFIGURATION FOR UNCHANNELIZED 8.192 MBIT/S H-MVIPDATA LOOPBACK40          |

PMC-Sierra, Inc.

TABLE 24 CONFIGURATION FOR BERT SIGNAL VERIFICATION TEST .... 42

PM2352 FREEDM™-32P672

DEVELOPMENT KIT BOARD USER MANUAL

DEVELOPMENT KIT BOARD USER MANUAL PMC-2001840

ISSUE 1

DEVELOPMENT KIT BOARD USER MANUAL

### 1 OVERVIEW

The FREEDM<sup>™</sup>-32P672 Development Kit consists of an add-on PCI card that can be used to test the functionality of the FREEDM<sup>™</sup>-32P672 chip. The PCI card consists of all the necessary components used for testing the various functions of the FREEDM<sup>™</sup>-32P672 device.

This document provides the necessary information for configuring the FREEDM<sup>™</sup>-32P672 Development Kit Board Rev 2.0. jumper settings.

### 1.1 Features

- The Development Kit supports a 33/66 MHz, 32 bit Peripheral Component Interconnect (PCI) 2.1 compliant bus for configuration, monitoring and transfer of packet data.

- The Development Kit supports both unchannelized H-MVIP as well as non-H-MVIP traffic. Channelized T1/E1 traffic on the 32 links is not directly supported since there is no provision for gapping of the link clocks. Channelized H-MVIP mode is not directly supported since the frame pulses are not generated on the Development Kit card.

- Channelized T1/E1 operation can be supported only with an external gapped clock (i.e. gapped clock from an external source). Channelized H-MVIP mode can be supported with external frame pulses and frame pulse clocks.

DEVELOPMENT KIT BOARD USER MANUAL PMC-2001840

DEVELOPMENT KIT BOARD USER MANUAL

### 2 HARDWARE CONFIGURATION

Jumper settings are used to configure the Development Kit board for various modes of operation. The supported modes include:

- Unchannelized T1 mode

- Unchannelized E1 mode

- Unchannelized 52 MHz mode

ISSUE 1

- Unchannelized 2.048 Mbit/s H-MVIP mode

- Mixed mode

For non-H-MVIP modes, only the following configurations can be achieved using jumper settings:

- 32 T1 links

- 32 E1 links

- 16 T1 links and 16 E1 links

- 3 DS-3/unchannelized 52 Mbit/s links

- Mixed mode 1 DS-3 link and T1/E1 links

With external gapped clock/frame pulse signals, channelized non H-MVIP as well as H-MVIP mode can be supported. This includes channelized 8 Mbit/s H-MVIP mode, for which an external frame pulse as well as frame pulse clocks are required. Note that the supplied software does not include support for includes channelized 8 Mbit/s H-MVIP mode. This section gives a detailed description of the jumper settings on the various headers.

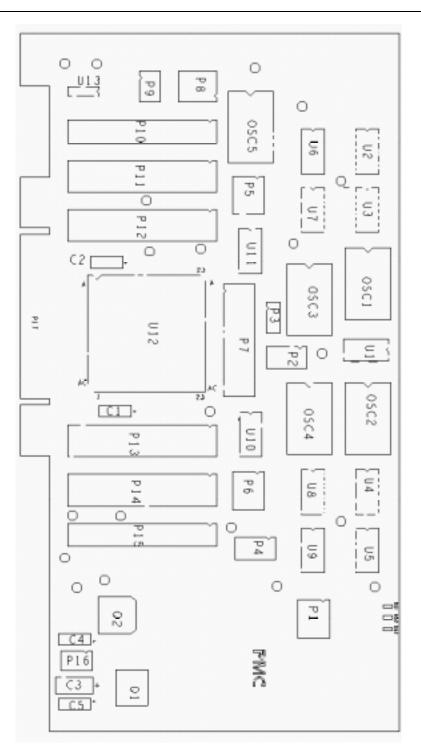

Figure 1 represents the block diagram for the FREEDM<sup>™</sup>-32P672 development kit board.

PMC-Sierra, Inc.

PM2352 FREEDM™-32P672

DEVELOPMENT KIT BOARD USER MANUAL PMC-2001840

ISSUE 1

DEVELOPMENT KIT BOARD USER MANUAL

## Figure 1 FREEDM<sup>™</sup>-32P672 Development Kit Board Diagram

DEVELOPMENT KIT BOARD USER MANUAL PMC-2001840

ISSUE 1

DEVELOPMENT KIT BOARD USER MANUAL

### 2.1 Voltage Selection

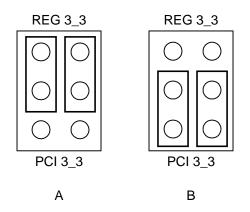

The FREEDM<sup>™</sup>-32P672 requires a 3.3 V source. The user has the option of using either the 3.3 V provided by the PCI connector or a board regulated 3.3 V source. The jumper settings for achieving these configurations are shown in Figure 2.

PMC-Sierra, Inc.

### Figure 2 3.3V Selection Header (P16).

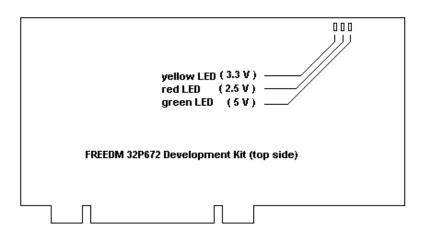

There are three LED's near the upper right corner on the topside of the Development Kit board. Plugging the Development Kit board into the PCI slot causes the green LED (indicating 5 V) to light upon power up. The two other LED's will light only if the 3.3 V source is selected. Figure 3 shows the location of these LED's on the board.

### Figure 3 LED's on the FREEDM<sup>™</sup>-32P672 Development Kit

DEVELOPMENT KIT BOARD USER MANUAL PMC-2001840 PMC-Sierra, Inc.

DEVELOPMENT KIT BOARD USER MANUAL

### 2.2 SYSCLK Jumper Setting

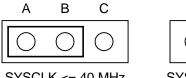

The SYSCLK input of the FREEDM<sup>™</sup>-32P672 chip can be provided with either a 40 MHz clock from an oscillator, or the PCICLKO clock output of the FREEDM<sup>™</sup>-32P672 chip (provided that a 33 MHz PCI bus is in use). The jumper settings on header P3 to achieve these configurations are shown in Figure 4. The jumper settings are also listed in Table 1.

| A | В          | С          |

|---|------------|------------|

| 0 | $\bigcirc$ | $\bigcirc$ |

|   |            |            |

SYSCLK <= 40 MHz

MHz SYSCLK <= PCICLKO

Figure 4 Jumper setting for SYSCLK (P3)

ISSUE 1

### Table 1Jumper setting for SYSCLK

| HEADER | JUMPER SETTING                    | CONFIGURATION          |

|--------|-----------------------------------|------------------------|

| P3     | Shorting jumper over pins A and B | SYSCLK from oscillator |

| P3     | Shorting jumper over pins B and C | SYSCLK from PCICLKO    |

Note: Pins B and C should only be shorted when the card is installed in a system with a 33 MHz PCI bus.

### 2.3 Jumper setting for RMVCK[3:0] provision

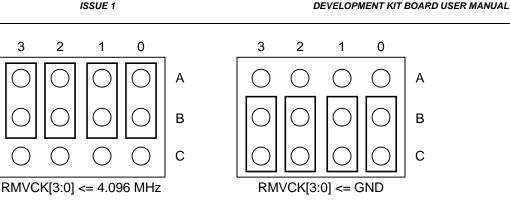

Each of the four RMVCK inputs to the FREEDM<sup>™</sup>-32P672 chip can be configured independently. Each RMVCK input to the FREEDM<sup>™</sup>-32P672 chip can either be grounded or provided with a 4.096 MHz clock from an oscillator. The jumper settings on header P5 to achieve these configurations are as shown in Figure 5. The jumper settings are also listed in Table 2.

In non-H-MVIP or 8.192 Mbit/s H-MVIP mode, RMVCK[3:0] should be grounded. To ground RMVCK[n] ( $0 \le n \le 3$ ), pin B-n should be shorted to pin C-n on header P5. 4.096 MHz clock from an oscillator can be provided to RMVCK[n] by shorting pins B-n and A-n. The jumper settings in Figure 5 (a) correspond to 4.096 MHz on RMVCK[3:0], whereas the jumper settings in Figure 5(b) correspond to grounded RMVCK[3:0].

DEVELOPMENT KIT BOARD USER MANUAL PMC-2001840

**ISSUE 1**

PMC-Sierra, Inc.

Note : Numbers written above the header represent the link groups.

#### Figure 5 Jumper settings for RMVCK[3:0] (P5).

#### Table 2 Jumper settings for RMVCK[3:0]

| HEADER | JUMPER SETTINGS               | CONFIGURATION                                |

|--------|-------------------------------|----------------------------------------------|

| P5     | Shorting jumper over pins A-n | 4.096 MHz input to RMVCK[n].                 |

|        | and B-n $(0 \le n \le 3)$     | $(0 \le n \le 3)$                            |

|        |                               | Unchannelized 2.048 Mbit/s H-<br>MVIP mode . |

| P5     | Shorting jumper over pins C-n | RMVCK[n] grounded.                           |

|        | and B-n $(0 \le n \le 3)$     | $(0 \le n \le 3)$                            |

|        |                               | Non – 2.048 Mbit/s H-MVIP mode.              |

Note : Each of the RMVCK inputs can be configured independent of the other RMVCK inputs.

For channelized 2.048 Mbit/s H-MVIP mode, external RMVCK should be provided by means of a wire to board connector plugged into pins of rows B and C on header P5. The ground plugs on the wire to board connector should mate with the ground pins (row C) on header P5.

#### 2.4 Jumper setting for TMVCK[3:0] provision

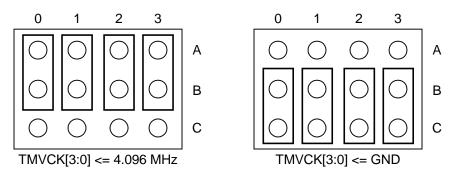

Similar to RMVCK, each of the four TMVCK inputs to the FREEDM<sup>™</sup>-32P672 device can be configured independently. Each TMVCK input to the FREEDM<sup>TM</sup>-

| RELEASED                                            | PMC     | PMC-Sierra, Inc. | PM2352 FREEDM™-32P672          |

|-----------------------------------------------------|---------|------------------|--------------------------------|

| DEVELOPMENT KIT BOARD USER<br>MANUAL<br>PMC-2001840 | ISSUE 1 | DEV              | ELOPMENT KIT BOARD USER MANUAL |

32P672 device can either be grounded or provided with a 4.096 MHz clock from an oscillator. The jumper settings on header P6 to achieve these configurations are shown in Figure 6. The jumper settings are also listed in Table 3.

In non-H-MVIP or 8.192 Mbit/s H-MVIP mode, TMVCK[3:0] should be grounded. To ground TMVCK[n] ( $0 \le n \le 3$ ), pin B-n should be shorted to pin C-n on header P6. The 4.096 MHz clock from an oscillator can be provided to TMVCK[n] by shorting pins B-n and A-n. The jumper settings in Figure 6(a) correspond to 4.096 MHz on TMVCK[3:0], whereas the jumper settings in Figure 6(b) correspond to grounded TMVCK[3:0].

Note : Numbers written above the header represent the link groups.

#### Jumper setting for TMVCK[3:0] (P6). Figure 6

#### Jumper setting for TMVCK[3:0] Table 3

| HEADER | JUMPER SETTINGS               | CONFIGURATION                                |

|--------|-------------------------------|----------------------------------------------|

| P6     | Shorting jumper over pins A-n | 4.096 MHz input to TMVCK[n].                 |

|        | and B-n $(0 \le n \le 3)$     | $(0 \le n \le 3)$                            |

|        |                               | Unchannelized 2.048 Mbit/s H-<br>MVIP mode . |

| P6     | Shorting jumper over pins C-n | TMVCK[n] grounded.                           |

|        | and B-n $(0 \le n \le 3)$     | $(0 \le n \le 3)$                            |

|        |                               | Non – 2.048 Mbit/s H-MVIP mode.              |

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS' INTERNAL USE 7

DEVELOPMENT KIT BOARD USER MANUAL PMC-2001840

PM2352 FREEDM™-32P672

ISSUE 1

DEVELOPMENT KIT BOARD USER MANUAL

Note : Each of the TMVCK inputs can be configured independent of the other TMVCK inputs.

For channelized 2.048 Mbit/s H-MVIP mode, external TMVCK is provided by means of a wire to board connector plugged into pins of rows B and C on header P6. The ground plugs on the wire to board connector should mate with the ground pins (row C) on header P6.

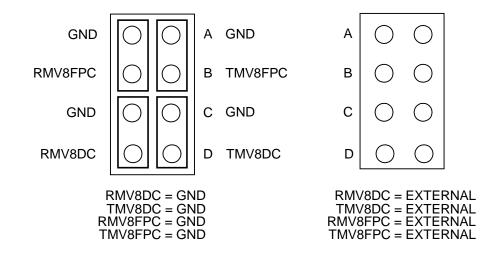

### 2.5 Jumper settings for TMV8DC, RMV8DC, TMV8FPC and RMV8FPC provision

The RMV8DC input to the FREEDM<sup>™</sup>-32P672 chip can either be grounded or provided with a 16.384 MHz clock from an external source by means of a wire to board connector. Similarly, the TMV8DC input to the FREEDM<sup>™</sup>-32P672 chip can either be grounded or provided with a 16.384 MHz clock from an external source. The RMV8FPC and TMV8FPC pins of the chip can either be grounded or provided with frame pulse clock signals from an external source. The jumper settings on header P4 to achieve these configurations are shown in Figure 7. They are also listed in Table 4.

In non-H-MVIP or 2.048 Mbit/s H-MVIP mode, TMV8DC and RMV8DC should be grounded. To ground these inputs, pins in row D should be shorted to corresponding pins in row C on header P4. Also, RMV8FPC and TMV8FPC should be grounded by shorting pins in row B to the corresponding pins in row A.

For 8.192 Mbit/s H-MVIP mode, external TMV8DC, RMV8DC, TMV8FPC and RMV8FPC should be provided by means of a wire to board connector plugged into pins on header P4. The ground plugs on the wire to board connector should mate with the ground pins (rows A and C) on header P4. Note that this mode is not presently supported in software.

PMC PMC-Sierra, Inc.

PM2352 FREEDM™-32P672

DEVELOPMENT KIT BOARD USER MANUAL PMC-2001840

ISSUE 1

DEVELOPMENT KIT BOARD USER MANUAL

Figure 7 Jumper settings for enabling of RMV8FPC, TMV8FPC, TMV8DC, and RMV8DC (P4)

# Table 4Jumper settings for enabling of RMV8FPC, TMV8FPC,TMV8DC, and RMV8DC

| HEADER | JUMPER SETTING                                                                                                     | CONFIGURATION                                                                                             |

|--------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| P4     | Pins in row A shorted to<br>corresponding pins in row B<br>Pins in row C shorted to<br>corresponding pins in row D | TMV8DC and RMV8DC grounded.<br>TMV8FPC and RMV8FPC grounded.<br>Non-8.192 Mbit/s H-MVIP mode.             |

| P4     | Wire to board connector<br>plugged into pins on header<br>P4.                                                      | 16.384 MHz clock provided to<br>RMV8DC and TMV8DC. 4.096 MHz<br>clock provided to RMV8FPC and<br>TMV8FPC. |

Note : The falling edges of RMV8FPC and TMV8FPC should be aligned respectively with the falling edges of RMV8DC and TMV8DC, with no more than 10 ns skew.

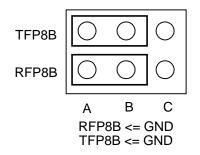

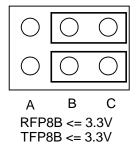

## 2.6 Jumper settings for TFP8B and RFP8B

TFP8B and RFP8B should be pulled down to ground when unchannelized 8.192 Mbit/s H-MVIP mode is not used. Both TFP8B and RFP8B should be pulled high for unchannelized 8.192 Mbit/s H-MVIP mode. The jumper settings on header P9 to achieve this configuration are shown in Figure 8. They are also listed in Table 5.

Non-8.192 Mbit/s H-MVIP Mode Unchannelized 8.192 Mbit/s H-MVIP Mode

### Figure 8 Jumper settings for RFP8B and TFP8B (P9)

### Table 5Jumper settings for RFP8B and TFP8B

| HEADER | JUMPER SETTING              | CONFIGURATION               |

|--------|-----------------------------|-----------------------------|

| P9     | Pins in column C shorted to | TFP8B and RFP8B pulled high |

DEVELOPMENT KIT BOARD USER MANUAL PMC-2001840

ISSUE 1

Note : RFPB for each link group can be independently configured with a single shorting jumper.

#### Jumper settings for RFPB[3:0] (P8) Figure 9

For channelized 2.048 Mbit/s H-MVIP mode, external RFPB[3:0] has to be provided by means of a wire to board connector plugged into pins of columns A and B on header P8. The ground plugs on the wire to board connector should mate with the ground pins (column A) on header P8.

## corresponding pips in column B (3.3 V)

|    |                                | (0.0 V).                        |

|----|--------------------------------|---------------------------------|

| P9 | Pins in column A shorted to    | TFP8B and RFP8B grounded.       |

|    | corresponding pins in column B | Non - 8.192 Mbit/s H-MVIP mode. |

|    |                                |                                 |

PMC-Sierra, Inc.

For 8.192 Mbit/s H-MVIP mode, external TFP8B and RFP8B have to be provided by means of a wire to board connector plugged into pins of columns A and B on header P9. The ground plugs on the wire to board connector should mate with the ground pins (column A) on header P9.

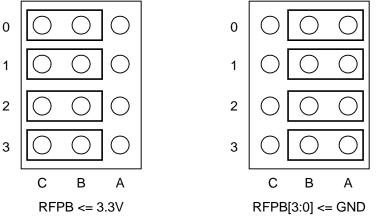

#### 2.7 Jumper settings for RFPB[3:0]

RFPB[3:0] should be pulled down to ground when unchannelized 2.048 Mbit/s H-MVIP mode is not used. If the links in one or more link groups are used for unchannelized 2.048 Mbit/s H-MVIP mode, RFPB inputs for these link groups should be pulled high. RFPB for each link group can be configured independently. The jumper settings on header P8 to achieve these configurations are listed in Figure 9. They are also listed in Table 6.

DEVELOPMENT KIT BOARD USER MANUAL

DEVELOPMENT KIT BOARD USER MANUAL PMC-2001840

ISSUE 1

DEVELOPMENT KIT BOARD USER MANUAL

| HEADER | JUMPER SETTINGS            | CONFIGURATION                     |

|--------|----------------------------|-----------------------------------|

| P8     | Pin A-n shorted to pin B-n | RFPB[n] grounded.                 |

|        | $(0 \le n \le 3)$          | $(0 \le n \le 3)$                 |

|        |                            | Non- 2.048 Mbit/s H-MVIP mode.    |

| P8     | Pin C-n shorted to pin B-n | RFPB[n] pulled high (3.3 V).      |

|        | $(0 \le n \le 3)$          | $(0 \le n \le 3)$                 |

|        |                            | Unchannelized 2.048 Mbit/s H-MVIP |

|        |                            | mode on link group n.             |

### Table 6 lumper settings for PEPR[3-0]

#### Jumper settings for TFPB[3:0] 2.8

TFPB[3:0] should be pulled down to ground when unchannelized 2.048 Mbit/s H-MVIP mode is not used. If the links in one or more link groups are used for unchannelized 2.048 Mbit/s H-MVIP mode, the TFPB inputs for these link groups should be pulled high. TFPB for each link group can be configured independently. The jumper settings on header P1 to achieve these configurations are listed in Figure 10. They are also listed in Table 7.

Note : TFPB for each link group can be independently configured with a single shorting jumper.

#### Jumper settings for TFPB[3:0] (P1) Figure 10

| Table 7 | Jumper settings for TFPB[3:0] |  |

|---------|-------------------------------|--|

|---------|-------------------------------|--|

| HEADER | JUMPER SETTINGS        | CONFIGURATION                  |

|--------|------------------------|--------------------------------|

| P1     | Pin A-n shorted to pin | TFPB[n] grounded .             |

|        | B-n                    | $(0 \le n \le 3)$              |

|        | (0 ≤ n ≤ 3)            | Non- 2.048 Mbit/s H-MVIP mode. |

| P1     | Pin C-n shorted to     | TFPB[n] pulled high (3.3 V).   |

PM2352 FREEDM™-32P672

DEVELOPMENT KIT BOARD USER MANUAL PMC-2001840

ISSUE 1

DEVELOPMENT KIT BOARD USER MANUAL

| HEADER | JUMPER SETTINGS        | CONFIGURATION                                               |

|--------|------------------------|-------------------------------------------------------------|

|        | pin B-n<br>(0 ≤ n ≤ 3) | $(0 \le n \le 3)$<br>Unchannelized 2.048 Mbit/s H-MVIP mode |

|        | (0 = 11 = 0)           | on link group n.                                            |

For channelized 2.048 Mbit/s H-MVIP mode, external TFPB[3:0] has to be provided by means of a wire to board connector plugged into pins of rows A and B on header P1. The ground plugs on the wire to board connector should mate with the ground pins (row A) on header P1.

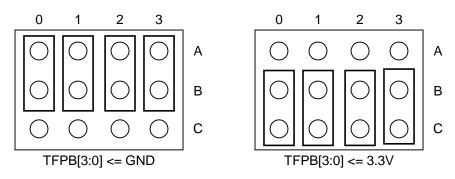

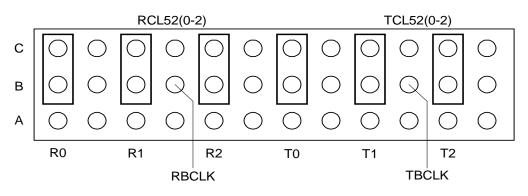

### 2.9 Jumper settings for selection of RCLK[2:0] and TCLK[2:0]

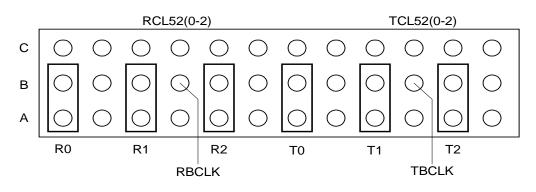

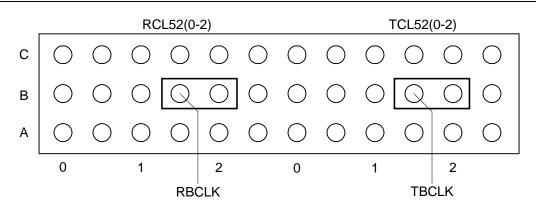

In non-H-MVIP mode, RCLK[2:0] and TCLK[2:0] can be set to either T1/E1 clock frequency or DS-3/52 MHz clock frequency. Jumper settings on header P7 to make this selection are listed in Table 8. Figure 11 shows how the jumpers are used on header P7.

A) T1/E1 Frequency on RCLK[2:0] and TCLK[2:0]

B) DS-3/52 MHz Frequency on RCLK[2:0] and TCLK[2:0]

PMC-Sierra, Inc.

RELEASED

ISSUE 1

DEVELOPMENT KIT BOARD USER MANUAL

### Figure 11 Jumper settings for selection of RCLK[2:0] and TCLK[2:0] (P7)

Note : The numbers T0, T1 and T2, corresponding to TCL52 (0-2) and R0, R1 and R2, corresponding to RCL52 (0-2), shown in Figure 11, respectively represent transmit and receive links 0, 1 and 2.

| Table 8 | Jumper settings for selection of RCLK[2:0] and TCLK[2:0] |

|---------|----------------------------------------------------------|

|---------|----------------------------------------------------------|

| HEADER | JUMPER SETTINGS                           | CONFIGURATION                |

|--------|-------------------------------------------|------------------------------|

| P7     | Pin A-Rn shorted to pin B-Rn              | DS-3/52 MHz frequency on     |

|        | $(0 \le n \le 2)$ under RCL52 (0-2) label | RCLK[2:0]                    |

| P7     | Pin C-Rn shorted to pin B-Rn              | T1/E1 frequency on RCLK[2:0] |

|        | $(0 \le n \le 2)$ under RCL52 (0-2) label |                              |

| P7     | Pin A-Tn shorted to pin B-Tn              | DS-3/52 MHz frequency on     |

|        | $(0 \le n \le 2)$ under TCL52 (0-2) label | TCLK[2:0]                    |

| P7     | Pin C-Tn shorted to pin B-Tn              | T1/E1 frequency on TCLK[2:0] |

|        | $(0 \le n \le 2)$ under TCL52 (0-2) label |                              |

Note : Each RCLK or TCLK selection can be configured independently.

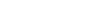

### 2.10 Jumper settings for enabling of RCLK[15:0]

RCLK[15:0] should be grounded when unchannelized H-MVIP mode is used on links 0 through 15. If one or more links from 0 through 15 is used for receiving non-H-MVIP traffic, the corresponding receive link clocks (i.e. RCLK[n] where  $0 \le n \le 15$ ) should be enabled. The jumper settings on header P12 for enabling RCLK[15:0] are listed in Table 9. Figure 12 shows the jumper settings for enabling all 16 receive link clocks from RCLK[15] through RCLK[0].

DEVELOPMENT KIT BOARD USER MANUAL PMC-2001840

ISSUE 1

DEVELOPMENT KIT BOARD USER MANUAL

Note : The pins for links from 0 through 15 are not in sequential order. Each of the RCLK inputs to FREEDM<sup>™</sup>-32P672 chip can be independently enabled.

### Figure 12 Jumper settings for enabling of RCLK[15:0] (P12)

| Table 9 | Jumper settings for enabling of RCLK[15:0] |

|---------|--------------------------------------------|

|---------|--------------------------------------------|

| HEADER | JUMPER SETTING             | CONFIGURATION               |

|--------|----------------------------|-----------------------------|

| P12    | Pin A-n shorted to pin B-n | RCLK[n] connected to        |

|        | (0 ≤ n ≤ 15)               | FREEDM <sup>™</sup> -32P672 |

|        |                            | (0 ≤ n ≤ 15)                |

| P12    | Pin C-n shorted to pin B-n | RCLK[n] grounded            |

|        | (0 ≤ n ≤ 15)               | (0 ≤ n ≤ 15)                |

DEVELOPMENT KIT BOARD USER MANUAL PMC-2001840

ISSUE 1

DEVELOPMENT KIT BOARD USER MANUAL

For channelized non-H-MVIP mode, externally gapped RCLK[15:0] should be provided by means of a wire to board connector plugged into pins of rows B and C on header P12. The ground plugs on the wire to board connector should mate with the ground pins (row C) on header P12.

PMC-Sierra, Inc.

### 2.11 Jumper settings for enabling of RCLK[31:16]

RCLK[31:16] should be grounded when unchannelized H-MVIP mode is used on links 16 through 31. If one or more links from 16 through 31 are used for receiving non-H-MVIP traffic, the corresponding receive link clocks (i.e. RCLK[n] where  $16 \le n \le 31$ ) should be enabled. The jumper settings on header P11 for enabling RCLK[31:16] are listed in Table 10. Figure 13 shows the jumper settings for enabling all 16 receive link clocks from RCLK[31] through RCLK[16].

### Table 10Jumper settings for enabling of RCLK[31:16]

| HEADER | JUMPER SETTING                                 | CONFIGURATION                                        |

|--------|------------------------------------------------|------------------------------------------------------|

| P11    | Pin A-n shorted to pin B-n $(16 \le n \le 31)$ | RCLK[n] connected to FREEDM <sup>™</sup> -<br>32P672 |

|        |                                                | (16 ≤ n ≤ 31)                                        |

| P11    | Pin C-n shorted to pin B-n                     | RCLK[n] grounded                                     |

|        | (16 ≤ n ≤ 31)                                  | $(16 \le n \le 31)$                                  |

For channelized non-H-MVIP mode, externally gapped RCLK[31:16] should be provided by means of a wire to board connector plugged into pins of rows B and C on header P11. The ground plugs on the wire to board connector should mate with the ground pins (row C) on header P11.

DEVELOPMENT KIT BOARD USER MANUAL PMC-2001840

ISSUE 1

P

DEVELOPMENT KIT BOARD USER MANUAL

MC PMC-Sierra, Inc.

Note : Each of the RCLK inputs to FREEDM<sup>TM</sup>-32P672 chip can be independently enabled.

### Figure 13 Jumper settings for enabling of RCLK[31:16] (P11)

DEVELOPMENT KIT BOARD USER MANUAL PMC-2001840

DEVELOPMENT KIT BOARD USER MANUAL

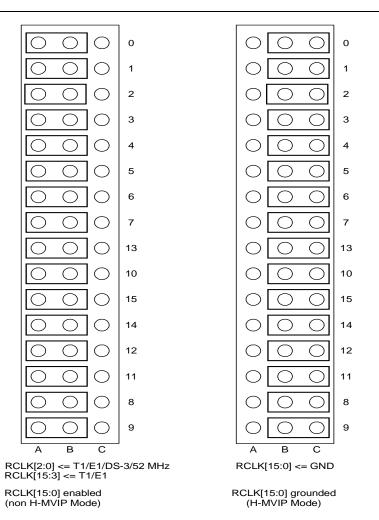

### 2.12 Jumper settings for enabling of TCLK[15:0]

ISSUE 1

TCLK[15:0] should be grounded when unchannelized H-MVIP mode is used on links 0 through 15. If one or more links from 0 through 15 is used for transmitting non-H-MVIP traffic, the corresponding transmit link clocks (i.e. TCLK[n] where 0  $\leq n \leq 15$ ) should be enabled. The jumper settings on header P13 for enabling TCLK[15:0] are listed in Table 11. Figure 14 shows the jumper settings for enabling all 16 transmit link clocks from TCLK[15] through TCLK[0].

Note : The pins for links 0 through 15 are not in sequential order. Each of the TCLK inputs to FREEDM<sup>™</sup>-32P672 chip can be independently enabled.

### Figure 14 Jumper settings for enabling of TCLK[15:0] (P13)

MANUAL PMC-2001840

DEVELOPMENT KIT BOARD USER

ISSUE 1

DEVELOPMENT KIT BOARD USER MANUAL

### Table 11Jumper settings for TCLK[15:0]

| HEADER | JUMPER SETTING             | CONFIGURATION                              |

|--------|----------------------------|--------------------------------------------|

| P13    | Pin A-n shorted to pin B-n | TCLK[n] connected to FREEDM <sup>™</sup> - |

|        | (0 ≤ n ≤ 15)               | 32P672                                     |

|        |                            | (0 ≤ n ≤ 15)                               |

| P13    | Pin C-n shorted to pin B-n | TCLK[n] grounded                           |

|        | (0 ≤ n ≤ 15)               | (0 ≤ n ≤ 15)                               |

For channelized non-H-MVIP mode, externally gapped TCLK[15:0] should be provided by means of a wire to board connector plugged into pins of rows B and C on header P13. The ground plugs on the wire to board connector should mate with the ground pins (row C) on header P13.

### 2.13 Jumper settings for enabling of TCLK[31:16]

TCLK[31:16] should be grounded when unchannelized H-MVIP mode is used on links 16 through 31. If one or more links from 16 through 31 are used for transmitting non-H-MVIP traffic, the corresponding transmit link clocks (i.e. TCLK[n] where  $16 \le n \le 31$ ) should be enabled. The jumper settings on header P14 for enabling TCLK[31:16] are listed in Table 12. Figure 15 shows the jumper settings for enabling all 16 transmit link clocks from TCLK[31] through TCLK[16].

For channelized non-H-MVIP mode, externally gapped TCLK[31:16] should be provided by means of a wire to board connector plugged into pins of rows B and C on header P14. The ground plugs on the wire to board connector should mate with the ground pins (row C) on header P14.

| HEADER | JUMPER SETTING             | CONFIGURATION                |

|--------|----------------------------|------------------------------|

| P14    | Pin A-n shorted to pin B-n | TCLK[n] connected to         |

|        | (16 ≤ n ≤ 31)              | FREEDM <sup>TM</sup> -32P672 |

|        |                            | (16 ≤ n ≤ 31)                |

| P14    | Pin C-n shorted to pin B-n | TCLK[n] grounded             |

|        | (16 ≤ n ≤ 31)              | (16 ≤ n ≤ 31)                |

Table 12

Jumper settings for enabling TCLK[31:16]

DEVELOPMENT KIT BOARD USER MANUAL PMC-2001840

ISSUE 1

P

DEVELOPMENT KIT BOARD USER MANUAL

MC PMC-Sierra, Inc.

### Figure 15 Jumper settings for TCLK[31:16] (P14)

MANUAL PMC-2001840

DEVELOPMENT KIT BOARD USER

PM2352 FREEDM™-32P672

ISSUE 1

DEVELOPMENT KIT BOARD USER MANUAL

### 2.14 Jumper settings for Data loopback on links 2 through 31

Data loopback can be performed on a per link basis on links 2 through 31. The jumper settings for loopback on these links, are listed in Table 13. Figure 16 shows the jumper settings for loopback on all the links from 2 to 31.

| Table 13 | Jumper settings for data loopback on links 2 through 31 |

|----------|---------------------------------------------------------|

|          |                                                         |

| HEADER | JUMPER SETTING                    | CONFIGURATION              |

|--------|-----------------------------------|----------------------------|

| P10    | Pins in row 'n' shorted with each | Loopback on link 'n'       |

|        | other (where $16 \le n \le 31$ )  | (where $16 \le n \le 31$ ) |

| P15    | Pins in row 'n' shorted with each | Loopback on link 'n'       |

|        | other (where $2 \le n \le 15$ )   | (where $2 \le n \le 15$ )  |

Note : Loopback can be performed on any link, independent of the other links. Pins on headers P10 and P15, corresponding to link 'n' (where  $2 \le n \le 31$ ), need not be shorted if loopback is not to be performed on link 'n'.

DEVELOPMENT KIT BOARD USER MANUAL PMC-2001840

ISSUE 1

DEVELOPMENT KIT BOARD USER MANUAL

PM2352 FREEDM™-32P672

PMC-Sierra, Inc.

Loopback on links 16 to 31

Loopback on links 2 to 15

### Figure 16 Jumper settings for data loopback on links 2 to 31

### 2.15 Jumper settings for Data loopback/cross-connect on links 0 and 1

Placement of shorting jumpers over header P2 result in configuration of either loopback or cross-connect of data on links 0 and 1. This is shown in Figure 17. The jumper settings are also listed in Table 14.

PMC PMC-Sierra, Inc.

PM2352 FREEDM™-32P672

DEVELOPMENT KIT BOARD USER MANUAL PMC-2001840

ISSUE 1

DEVELOPMENT KIT BOARD USER MANUAL

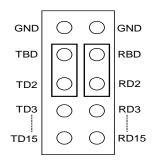

Figure 17 Jumper settings for loopback/cross-connect on links 0 and 1 (P2)

| Table 14 Jumper settings for loopback/cross-connect on links 0 a | and 1 |

|------------------------------------------------------------------|-------|

|------------------------------------------------------------------|-------|

| HEADER | JUMPER SETTING                            | CONFIGURATION                  |

|--------|-------------------------------------------|--------------------------------|

| P2     | TD0 shorted to RD1,<br>TD1 shorted to RD0 | Cross-connect on links 0 and 1 |

| P2     | TD0 shorted to RD0,<br>TD1 shorted to RD1 | Loopback on links 0 and 1      |

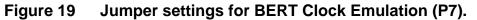

### 2.16 Jumper settings for BERT Emulation

Link 2 is used to emulate the BERT interface. To emulate BERT interface, link 2 should act as the source of TBD data, and at the same time, receive data on RBD output of FREEDM<sup>TM</sup>-32P672 chip. RBCLK and TBCLK are respectively shorted to RCLK[2] and TCLK[2]. The jumper settings on headers P15 and P7 for BERT Emulation are listed in Table 15 and are also shown in Figure 18 and Figure 19.

### Figure 18 Jumper settings for BERT data emulation (P15)

DEVELOPMENT KIT BOARD USER MANUAL PMC-2001840

ISSUE 1

P

DEVELOPMENT KIT BOARD USER MANUAL

| Table 15 Jumper settings for | r BERT Clock Emulation |

|------------------------------|------------------------|

|------------------------------|------------------------|

| HEADER | JUMPER SETTING                          | CONFIGURATION            |

|--------|-----------------------------------------|--------------------------|

| P15    | TD2 shorted to TBD, BERT data emulation |                          |

|        | RD2 shorted to RBD                      |                          |

| P7     | Pin B2 (under RCL52(0-2) )              | RBCLK shorted to RCLK[2] |

|        | shorted to RBCLK.                       |                          |

| P7     | Pin B2 (under TCL52(0-2) )              | TBCLK shorted to TCLK[2] |

|        | shorted to TBCLK.                       |                          |

### 2.17 Placement of oscillators in the sockets

Table 16 lists the oscillators to be placed in the sockets, prior to the card being plugged into the socket.

| Table 16 | Oscillator | placement in sockets |

|----------|------------|----------------------|

|----------|------------|----------------------|

| SOCKET | OSCILLATOR<br>FREQUENCY | TEST CASE                                                |

|--------|-------------------------|----------------------------------------------------------|

| OSC 1  | 1.544 MHz               | Unchannelized T1 on links 0 through 15                   |

|        | 2.048 MHz               | Unchannelized E1 on links 0 through 15                   |

| OSC 2  | 4.096 MHz               | Unchannelized 2.048 Mbit/s H-MVIP mode                   |

| OSC 3  | 52 MHz                  | Unchannelized 52 Mbit/s traffic on links 0 through 2     |

|        | 44.736 MHz              | Unchannelized 44.736 Mbit/s traffic on links 0 through 2 |

| OSC 4  | 1.544 MHz               | Unchannelized T1 on links 16 through 31                  |

|        | 2.048 MHz               | Unchannelized E1 on links 16 through 31                  |

| OSC 5  | 40 MHz                  | SYSCLK for FREEDM <sup>™</sup> -32P672                   |

DEVELOPMENT KIT BOARD USER MANUAL PMC-2001840

ISSUE 1

DEVELOPMENT KIT BOARD USER MANUAL

Note: Clocks are not provisioned to the clock inputs of the FREEDM<sup>™</sup>-32P672 chip simply by placing the oscillators in the appropriate sockets. Frequency selection and clock provision has to be done by means of jumpers, as mentioned in earlier sections.

MANUAL PMC-2001840

DEVELOPMENT KIT BOARD USER

ISSUE 1

### **<u>3</u>** CONFIGURATIONS FOR THE TEST CASES

### 3.1 Configuration for PCI Interface Test

Table 17 lists the required configuration for the PCI Interface Test.

| Table 17 | Configuration for the PCI Interface Test |

|----------|------------------------------------------|

|          |                                          |

| HEADER | SIGNAL               | JUMPER                                                                         | CONFIGURATION ACHIEVED                                                        |

|--------|----------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| P3     | SYSCLK               | SETTINGS<br>Jumper over pins B<br>and C                                        | SYSCLK connected to<br>PCICLKO (only for 33 MHz<br>operation)                 |

| P5     | RMVCK[3:0]           | Pins B0, B1, B2<br>and B3 shorted to<br>pins C0, C1, C2<br>and C3 respectively | RMVCK[3:0] grounded                                                           |

| P6     | TMVCK[3:0]           | Pins B0, B1, B2<br>and B3 shorted to<br>pins C0, C1, C2<br>and C3 respectively | TMVCK[3:0] grounded                                                           |

| P4     | RMV8DC &<br>TMV8DC   | Pins in row C<br>shorted to pins in<br>row D respectively                      | RMV8DC &TMV8DC<br>grounded                                                    |

| P4     | RMV8FPC &<br>TMV8FPC | Pins in row A<br>shorted to pins in<br>row B respectively                      | RMV8FPC & TMV8FPC<br>grounded                                                 |

| P8     | RFPB[3:0]            | Pins A0, A1, A2 and<br>A3 shorted to pins<br>B0, B1, B2 and B3<br>respectively | RFPB[3:0] grounded                                                            |

| P1     | TFPB[3:0]            | Pins A0, A1, A2 and<br>A3 shorted to pins<br>B0, B1, B2 and B3<br>respectively | TFPB[3:0] grounded                                                            |

| P9     | RFP8B &<br>TFP8B     | Pins in row A<br>shorted to pins in<br>row B respectively                      | RFP8B and TFP8B grounded                                                      |

| P12    | RCLK[15:0]           | Pins A0 through<br>A15 shorted to pins<br>B0 through B15<br>respectively       | 1.544 MHz provision to<br>RCLK[15:0] inputs of<br>FREEDM <sup>™</sup> -32P672 |

| P11    | RCLK[31:16]          | Pins A16 through                                                               | 1.544 MHz provision to                                                        |

PM2352 FREEDM™-32P672

DEVELOPMENT KIT BOARD USER MANUAL PMC-2001840

ISSUE 1

DEVELOPMENT KIT BOARD USER MANUAL

| h   |                 |                                                                                                                  |                                                                   |

|-----|-----------------|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

|     |                 | A31 shorted to pins<br>B16 through B31<br>respectively                                                           | RCLK[31:16] inputs of<br>FREEDM <sup>™</sup> -32P672              |

| P13 | TCLK[15:0]      | Pins A0 through<br>A15 shorted to pins<br>B0 through B15<br>respectively                                         | 1.544 MHz provision to<br>TCLK[15:0] inputs of<br>FREEDM™-32P672  |

| P14 | TCLK[31:16]     | Pins A16 through<br>A31 shorted to pins<br>B16 through B31<br>respectively                                       | 1.544 MHz provision to<br>TCLK[31:16] inputs of<br>FREEDM™-32P672 |

| P7  | RCL52[2:0]      | Pins B-R0, B-R1<br>and B-R2 shorted<br>to pins C-R0, C-R1<br>and C-R2<br>respectively<br>(Columns 0, 1 and<br>2) | 1.544 MHz selection for<br>RCLK[2:0]                              |

| P7  | TCL52[2:0]      | Pins B-T0, B-T1<br>and B-T2 shorted<br>to pins C-T0, C-T1<br>and C-T2<br>respectively<br>(Columns 0, 1 and<br>2) | 1.544 MHz selection for<br>TCLK[2:0]                              |

| P15 | TD RD[15:2]     | Jumpers not used                                                                                                 | No loopback on links 2 through 15                                 |

| P10 | TD<br>RD[31:16] | Jumpers not used                                                                                                 | No loopback on links 16<br>through 31                             |

| P2  | TD RD[1:0]      | Jumpers not used                                                                                                 | No loopback on links 0 and 1                                      |

### 3.2 Configuration for unchannelized T1 loopback mode

Each of the 32 transmit/receive links can be configured independently to transmit/receive unchannelized T1 data. This is done by the software. Loopback can be performed on any of these 32 links by using shorting jumpers appropriately over headers provided on the PCI card. Table 18 shows the jumper settings for performing loopback on all the 32 links.

| Table 18 | Configuration for simultaneous loopback of T1 data of | n 32 links |

|----------|-------------------------------------------------------|------------|

|----------|-------------------------------------------------------|------------|

| HEADER | SIGNAL | JUMPER | CONFIGURATION ACHIEVED |

|--------|--------|--------|------------------------|

|        |        |        |                        |

PM2352 FREEDM™-32P672

DEVELOPMENT KIT BOARD USER MANUAL PMC-2001840

ISSUE 1

DEVELOPMENT KIT BOARD USER MANUAL

|     |                      | SETTINGS                                                                       |                                                                                |

|-----|----------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| P3  | SYSCLK               | Jumper over pins B<br>and C                                                    | SYSCLK connected to<br>PCICLKO (only for 33 MHz<br>operation)                  |

| P5  | RMVCK[3:0]           | Pins B0, B1, B2<br>and B3 shorted to<br>pins C0, C1, C2<br>and C3 respectively | RMVCK[3:0] grounded                                                            |

| P6  | TMVCK[3:0]           | Pins B0, B1, B2<br>and B3 shorted to<br>pins C0, C1, C2<br>and C3 respectively | TMVCK[3:0] grounded                                                            |

| P4  | RMV8DC &<br>TMV8DC   | Pins in row C<br>shorted to pins in<br>row D respectively                      | RMV8DC &TMV8DC<br>grounded                                                     |

| P4  | RMV8FPC &<br>TMV8FPC | Pins in row A<br>shorted to pins in<br>row B respectively                      | RMV8FPC & TMV8FPC<br>grounded                                                  |

| P8  | RFPB[3:0]            | Pins A0, A1, A2 and<br>A3 shorted to pins<br>B0, B1, B2 and B3<br>respectively | RFPB[3:0] grounded                                                             |

| P1  | TFPB[3:0]            | Pins A0, A1, A2 and<br>A3 shorted to pins<br>B0, B1, B2 and B3<br>respectively | TFPB[3:0] grounded                                                             |

| P9  | RFP8B &<br>TFP8B     | Pins in row A<br>shorted to pins in<br>row B respectively                      | RFP8B and TFP8B grounded                                                       |

| P12 | RCLK[15:0]           | Pins A0 through<br>A15 shorted to pins<br>B0 through B15<br>respectively       | 1.544 MHz provision to<br>RCLK[15:0] inputs of<br>FREEDM™-32P672               |

| P11 | RCLK[31:16]          | Pins A16 through<br>A31 shorted to pins<br>B16 through B31<br>respectively     | 1.544 MHz provision to<br>RCLK[31:16] inputs of<br>FREEDM™-32P672              |

| P13 | TCLK[15:0]           | Pins A0 through<br>A15 shorted to pins<br>B0 through B15<br>respectively       | 1.544 MHz provision to<br>TCLK[15:0] inputs of<br>FREEDM™-32P672               |

| P14 | TCLK[31:16]          | Pins A16 through<br>A31 shorted to pins<br>B16 through B31                     | 1.544 MHz provision to<br>TCLK[31:16] inputs of<br>FREEDM <sup>™</sup> -32P672 |

PM2352 FREEDM™-32P672

DEVELOPMENT KIT BOARD USER MANUAL PMC-2001840

ISSUE 1

DEVELOPMENT KIT BOARD USER MANUAL

| . <u> </u> | 1               |                                                                                                                  |                                      |

|------------|-----------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------|

|            |                 | respectively                                                                                                     |                                      |

| P7         | RCL52[2:0]      | Pins B-R0, B-R1<br>and B-R2 shorted<br>to pins C-R0, C-R1<br>and C-R2<br>respectively<br>(Columns 0, 1 and<br>2) | 1.544 MHz selection for<br>RCLK[2:0] |

| P7         | TCL52[2:0]      | Pins B-T0, B-T1<br>and B-T2 shorted<br>to pins C-T0, C-T1<br>and C-T2<br>respectively<br>(Columns 0, 1 and<br>2) | 1.544 MHz selection for<br>TCLK[2:0] |

| P15        | TD RD[15:2]     | Pins A2 through<br>A15 shorted to pins<br>B2 through B15<br>respectively                                         | Loopback on links 2 through<br>15    |

| P10        | TD<br>RD[31:16] | Pins A16 through<br>A31 shorted to pins<br>B16 through B31<br>respectively                                       | Loopback on links 16 through 31      |

| P2         | TD RD[1:0]      | TD0 shorted to<br>RD0, TD1 shorted<br>to RD1                                                                     | Loopback on links 0 and 1            |

Note: 1.544 MHz oscillators should be placed in sockets OSC 1 and OSC 4. If loopback is not to be performed on each of the 32 links, jumper settings will be similar to those shown in Table 18, except for the unused RCLK, TCLK, RD and TD. Unused RCLK and TCLK should be grounded by placing jumpers over pins of columns B and C, of the unused links. Unused RD and TD need not be shorted.

### 3.3 Configuration for unchannelized E1 loopback mode

Each of the 32 transmit/receive links can be configured independently to transmit/receive unchannelized E1 data. This is done by the software. Loopback can be performed on any of these 32 links by using shorting jumpers

MANUAL PMC-2001840

DEVELOPMENT KIT BOARD USER

ISSUE 1

DEVELOPMENT KIT BOARD USER MANUAL

appropriately over headers provided on the PCI card. Table 18 shows the jumper settings for performing loopback on all the 32 links.

## Table 18Configuration for simultaneous loopback of E1 data on 32<br/>links

| HEADER | SIGNAL               | JUMPER<br>SETTINGS                                                                | CONFIGURATION ACHIEVED                                                        |

|--------|----------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| P3     | SYSCLK               | Jumper over pins<br>B and C                                                       | SYSCLK connected to<br>PCICLKO<br>(only for 33 MHz operation)                 |

| P5     | RMVCK[3:0]           | Pins B0, B1, B2<br>and B3 shorted to<br>pins C0, C1, C2<br>and C3<br>respectively | RMVCK[3:0] grounded                                                           |

| P6     | TMVCK[3:0]           | Pins B0, B1, B2<br>and B3 shorted to<br>pins C0, C1, C2<br>and C3<br>respectively | TMVCK[3:0] grounded                                                           |

| P4     | RMV8DC &<br>TMV8DC   | Pins in row C<br>shorted to pins in<br>row D respectively                         | RMV8DC &TMV8DC grounded                                                       |

| P4     | RMV8FPC &<br>TMV8FPC | Pins in row A<br>shorted to pins in<br>row B respectively                         | RMV8FPC & TMV8FPC<br>grounded                                                 |

| P8     | RFPB[3:0]            | Pins A0, A1, A2<br>and A3 shorted to<br>pins B0, B1, B2<br>and B3<br>respectively | RFPB[3:0] grounded                                                            |

| P1     | TFPB[3:0]            | Pins A0, A1, A2<br>and A3 shorted to<br>pins B0, B1, B2<br>and B3<br>respectively | TFPB[3:0] grounded                                                            |

| P9     | RFP8B &<br>TFP8B     | Pins in column A<br>shorted to pins in<br>column B<br>respectively                | RFP8B and TFP8B grounded                                                      |

| P12    | RCLK[15:0]           | Pins A0 through<br>A15 shorted to<br>pins B0 through                              | 2.048 MHz provision to<br>RCLK[15:0] inputs of<br>FREEDM <sup>™</sup> -32P672 |

PM2352 FREEDM™-32P672

DEVELOPMENT KIT BOARD USER MANUAL PMC-2001840

ISSUE 1

DEVELOPMENT KIT BOARD USER MANUAL

|             |             | D15 roop a thirdy i |                                |

|-------------|-------------|---------------------|--------------------------------|

| <b>D</b> 44 |             | B15 respectively    |                                |

| P11         | RCLK[31:16] | Pins A16 through    | 2.048 MHz provision to         |

|             |             | A31 shorted to      | RCLK[31:16] inputs of          |

|             |             | pins B16 through    | FREEDM <sup>™</sup> -32P672    |

|             |             | B31 respectively    |                                |

| P13         | TCLK[15:0]  | Pins A0 through     | 2.048 MHz provision to         |

|             |             | A15 shorted to      | TCLK[15:0] inputs of           |

|             |             | pins B0 through     | FREEDM <sup>TM</sup> -32P672   |

|             |             | B15 respectively    |                                |

| P14         | TCLK[31:16] | Pins A16 through    | 2.048 MHz provision to         |

|             |             | A31 shorted to      | TCLK[31:16] inputs of          |

|             |             | pins B16 through    | FREEDM <sup>™</sup> -32P672    |

|             |             | B31 respectively    |                                |

| P7          | RCL52[2:0]  | Pins B-R0, B-R1     | 2.048 MHz selection for        |

|             |             | and B-R2 shorted    | RCLK[2:0]                      |

|             |             | to pins C-R0, C-R1  |                                |

|             |             | and C-R2            |                                |

|             |             | respectively        |                                |

|             |             | (Columns 0, 1 and   |                                |

|             |             | 2)                  |                                |

| P7          | TCL52[2:0]  | Pins B-T0, B-T1     | 2.048 MHz selection for        |

|             |             | and B-T2 shorted    | TCLK[2:0]                      |

|             |             | to pins C-T0, C-T1  |                                |

|             |             | and C-T2            |                                |

|             |             | respectively        |                                |

|             |             | (Columns 0, 1 and   |                                |

|             |             | 2)                  |                                |

| P15         | TD RD[15:2] | Pins A2 through     | Loopback on links 2 through 15 |

|             |             | A15 shorted to      |                                |

|             |             | pins B2 through     |                                |

|             |             | B15 respectively    |                                |

| P10         | TD          | Pins A16 through    | Loopback on links 16 through   |

|             | RD[31:16]   | A31 shorted to      | 31                             |

|             |             | pins B16 through    |                                |

|             |             | B31 respectively    |                                |

| P2          | TD RD[1:0]  | TD0 shorted to      | Loopback on links 0 and 1      |

|             |             | RD0, TD1 shorted    |                                |

|             | 1           | to RD1              |                                |

Note: 2.048 MHz oscillators should be placed in sockets OSC 1 and OSC 4. If loopback is not to be performed on each of the 32 links, jumper settings will be similar to those shown in Table 18, except for the unused RCLK, TCLK, RD and TD. Unused RCLK and TCLK should be grounded by placing shorting jumpers

DEVELOPMENT KIT BOARD USER MANUAL PMC-2001840

DEVELOPMENT KIT BOARD USER MANUAL

over pins of columns B and C, of the unused links. Unused RD and TD need not be shorted.

## 3.4 Configuration for 16 T1/ 16 E1 unchannelized loopback mode

ISSUE 1

With 1.544 MHz oscillator placed in socket OSC 1, and 2.048 MHz oscillator placed in OSC 4, simultaneous loopback of 16 unchannelized T1 links (links 0-15) and 16 unchannelized E1 links (links 16-31) can be performed. The jumper settings for this loopback are shown in Table 19.

| Table 19 | Configuration for 16 T1/E1 unchannelized loopback |

|----------|---------------------------------------------------|

|----------|---------------------------------------------------|

| HEADER | SIGNAL               | JUMPER<br>SETTINGS                                                             | CONFIGURATION ACHIEVED                                        |

|--------|----------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------|

| P3     | SYSCLK               | Jumper over pins B<br>and C                                                    | SYSCLK connected to<br>PCICLKO (only for 33 MHz<br>operation) |

| P5     | RMVCK[3:0]           | Pins B0, B1, B2<br>and B3 shorted to<br>pins C0, C1, C2<br>and C3 respectively | RMVCK[3:0] grounded                                           |

| P6     | TMVCK[3:0]           | Pins B0, B1, B2<br>and B3 shorted to<br>pins C0, C1, C2<br>and C3 respectively | TMVCK[3:0] grounded                                           |

| P4     | RMV8DC &<br>TMV8DC   | Pins in row C<br>shorted to pins in<br>row D respectively                      | RMV8DC &TMV8DC<br>grounded                                    |

| P4     | RMV8FPC &<br>TMV8FPC | Pins in row A<br>shorted to pins in<br>row B respectively                      | RMV8FPC & TMV8FPC<br>grounded                                 |

| P8     | RFPB[3:0]            | Pins A0, A1, A2 and<br>A3 shorted to pins<br>B0, B1, B2 and B3<br>respectively | RFPB[3:0] grounded                                            |

| P1     | TFPB[3:0]            | Pins A0, A1, A2 and<br>A3 shorted to pins<br>B0, B1, B2 and B3<br>respectively | TFPB[3:0] grounded                                            |

| P9     | RFP8B &<br>TFP8B     | Pins in column A<br>shorted to pins in<br>column B<br>respectively             | RFP8B and TFP8B grounded                                      |

| P12    | RCLK[15:0]           | Pins A0 through                                                                | 1.544 MHz provision to                                        |

PM2352 FREEDM™-32P672

DEVELOPMENT KIT BOARD USER MANUAL PMC-2001840

ISSUE 1

DEVELOPMENT KIT BOARD USER MANUAL

|     |                 | A15 shorted to pins<br>B0 through B15<br>respectively                                                            | RCLK[15:0] inputs of<br>FREEDM <sup>™</sup> -32P672                            |

|-----|-----------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| P11 | RCLK[31:16]     | Pins A16 through<br>A31 shorted to pins<br>B16 through B31<br>respectively                                       | 2.048 MHz provision to<br>RCLK[31:16] inputs of<br>FREEDM <sup>™</sup> -32P672 |

| P13 | TCLK[15:0]      | Pins A0 through<br>A15 shorted to pins<br>B0 through B15<br>respectively                                         | 1.544 MHz provision to<br>TCLK[15:0] inputs of<br>FREEDM™-32P672               |

| P14 | TCLK[31:16]     | Pins A16 through<br>A31 shorted to pins<br>B16 through B31<br>respectively                                       | 2.048 MHz provision to<br>TCLK[31:16] inputs of<br>FREEDM <sup>™</sup> -32P672 |

| P7  | RCL52[2:0]      | Pins B-R0, B-R1<br>and B-R2 shorted<br>to pins C-R0, C-R1<br>and C-R2<br>respectively<br>(Columns 0, 1 and<br>2) | 1.544 MHz selection for<br>RCLK[2:0]                                           |

| P7  | TCL52[2:0]      | Pins B-T0, B-T1<br>and B-T2 shorted<br>to pins C-T0, C-T1<br>and C-T2<br>respectively<br>(Columns 0, 1 and<br>2) | 1.544 MHz selection for<br>TCLK[2:0]                                           |

| P15 | TD RD[15:2]     | Pins A2 through<br>A15 shorted to pins<br>B2 through B15<br>respectively                                         | Loopback on links 2 through<br>15                                              |

| P10 | TD<br>RD[31:16] | Pins A16 through<br>A31 shorted to pins<br>B16 through B31<br>respectively                                       | Loopback on links 16 through 31                                                |

| P2  | TD RD[1:0]      | TD0 shorted to<br>RD0, TD1 shorted<br>to RD1                                                                     | Loopback on links 0 and 1                                                      |

Note: If links 0 through 15 are to be configured for unchannelized E1 data and links 16 through 31 are to be configured for T1 data, 2.048 MHz oscillator should

DEVELOPMENT KIT BOARD USER

ISSUE 1

DEVELOPMENT KIT BOARD USER MANUAL

be placed in socket OSC 1, whereas 1.544 MHz oscillator should be placed in OSC 4.

## 3.5 Configuration for unchannelized 52 Mbit/s

Links 0 through 2 can be configured for supporting 52 Mbit/s data. The jumper settings for simultaneous loopback of 52 Mbit/s on links 0 through 2, is shown in Table 20.

# Table 20Simultaneous loopback of unchannelized 52 Mbit/s data on<br/>links 0 through 2

| HEADER | SIGNAL               | JUMPER<br>SETTINGS                                                             | CONFIGURATION ACHIEVED                                                  |

|--------|----------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| P3     | SYSCLK               | Jumper over pins B<br>and A                                                    | SYSCLK set to 40 MHz                                                    |

| P5     | RMVCK[3:0]           | Pins B0, B1, B2<br>and B3 shorted to<br>pins C0, C1, C2<br>and C3 respectively | RMVCK[3:0] grounded                                                     |

| P6     | TMVCK[3:0]           | Pins B0, B1, B2<br>and B3 shorted to<br>pins C0, C1, C2<br>and C3 respectively | TMVCK[3:0] grounded                                                     |

| P4     | RMV8DC &<br>TMV8DC   | Pins in row C<br>shorted to pins in<br>row D respectively                      | RMV8DC &TMV8DC<br>grounded                                              |

| P4     | RMV8FPC &<br>TMV8FPC | Pins in row A<br>shorted to pins in<br>row B respectively                      | RMV8FPC & TMV8FPC grounded                                              |

| P8     | RFPB[3:0]            | Pins A0, A1, A2 and<br>A3 shorted to pins<br>B0, B1, B2 and B3<br>respectively | RFPB[3:0] grounded                                                      |

| P1     | TFPB[3:0]            | Pins A0, A1, A2 and<br>A3 shorted to pins<br>B0, B1, B2 and B3<br>respectively | TFPB[3:0] grounded                                                      |

| P9     | RFP8B &<br>TFP8B     | Pins in column A<br>shorted to pins in<br>column B<br>respectively             | RFP8B and TFP8B grounded                                                |

| P12    | RCLK[15:0]           | Pins Ay shorted to pins By                                                     | 52 MHz provision to RCLK[2:0]<br>inputs of FREEDM <sup>™</sup> -32P672. |

DEVELOPMENT KIT BOARD USER MANUAL PMC-2001840

ISSUE 1

DEVELOPMENT KIT BOARD USER MANUAL

| D44 |                 | respectively, where<br>y = link to be<br>operated at 52 MHz<br>The pins Bz<br>shorted to pins Cz<br>where z = link to be<br>disabled                                  | (select 2 links to provision,<br>disable the third)                                                                                |

|-----|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| P11 | RCLK[31:16]     | Pins C16 through<br>C31 shorted to pins<br>B16 through B31<br>respectively                                                                                            | RCLK[31:16] grounded                                                                                                               |

| P13 | TCLK[15:0]      | Pins Ay shorted to<br>pins By<br>respectively, where<br>y = link to be<br>operated at 52Mhz.<br>The pins Bz<br>shorted to pins Cz<br>where z = link to be<br>disabled | 52 MHz provision to TCLK[2:0]<br>inputs of FREEDM <sup>™</sup> -32P672.<br>( select 2 links to provision and<br>disable the third) |

| P14 | TCLK[31:16]     | Pins C16 through<br>C31 shorted to pins<br>B16 through B31<br>respectively                                                                                            | TCLK[31:16] grounded                                                                                                               |

| P7  | RCL52[2:0]      | Pins A-R0, A-R1<br>and A-R2 shorted<br>to pins B-R0, B-R1<br>and B-R2<br>respectively<br>(Columns 0, 1 and<br>2)                                                      | 52 MHz selection for<br>RCLK[2:0]                                                                                                  |

| P7  | TCL52[2:0]      | Pins B-T0, B-T1<br>and B-T2 shorted<br>to pins A-T0, A-T1<br>and A-T2<br>respectively<br>(Columns 0, 1 and<br>2)                                                      | 52 MHz selection for<br>TCLK[2:0]                                                                                                  |

| P15 | TD RD[15:2]     | Pin A2 shorted to pin B2 respectively                                                                                                                                 | Loopback on link 2                                                                                                                 |

| P10 | TD<br>RD[31:16] | Jumpers not used                                                                                                                                                      | No loopback on links 16<br>through 31                                                                                              |

| P2  | TD RD[1:0]      | TD0 shorted to<br>RD0, TD1 shorted                                                                                                                                    | Loopback on links 0 and 1                                                                                                          |

DEVELOPMENT KIT BOARD USER MANUAL PMC-2001840

should be grounded.

RD0, on header P2.

ISSUE 1

## Note 3: Software support is provided for 52Mbit/s data loopback on only 2 of the 3 possible links, RCLK and TCLK inputs for the third link should be disabled. Also, SYSCLK can be connected to PCICLKO output of the FREEDM<sup>™</sup>-32P672

chip, provided that PCI frequency is 33 MHz.

to RD1

#### Configuration for unchannelized Mixed DS3/T1/E1 data loopback 3.6

Links 0 through 2 can be configured for supporting DS-3 data. The jumper settings for simultaneous loopback of Mixed DS3/T1/E1, is shown in Table 21

| HEADER | SIGNAL               | JUMPER<br>SETTINGS                                                             | CONFIGURATION ACHIEVED        |

|--------|----------------------|--------------------------------------------------------------------------------|-------------------------------|

| P3     | SYSCLK               | Jumper over pins B<br>and A                                                    | SYSCLK set to 40 MHz          |

| P5     | RMVCK[3:0]           | Pins B0, B1, B2<br>and B3 shorted to<br>pins C0, C1, C2<br>and C3 respectively | RMVCK[3:0] grounded           |

| P6     | TMVCK[3:0]           | Pins B0, B1, B2<br>and B3 shorted to<br>pins C0, C1, C2<br>and C3 respectively | TMVCK[3:0] grounded           |

| P4     | RMV8DC &<br>TMV8DC   | Pins in row C<br>shorted to pins in<br>row D respectively                      | RMV8DC &TMV8DC<br>grounded    |

| P4     | RMV8FPC &<br>TMV8FPC | Pins in row A<br>shorted to pins in<br>row B respectively                      | RMV8FPC & TMV8FPC<br>grounded |

| P8     | RFPB[3:0]            | Pins A0, A1, A2 and                                                            | RFPB[3:0] grounded            |

### Table 21 Simultaneous loopback of unchannelized Mixed DS3/T1/E1 data

Note 1: All unused RCLK and TCLK should be grounded, by placing shorting jumpers over pins of columns B and C, of the unused links. Shorting jumpers need not be placed over receive/transmit links 3 through 31 (RD[31:3] and TD[31:3]). If not all three RCLK and TCLK are used, unused RCLK and TCLK

performed. TD0 should be shorted to RD1, whereas TD1 should be shorted to

Note 2: If simultaneous cross-connect of data on links 0 and 1 is to be

PM2352 FREEDM™-32P672

DEVELOPMENT KIT BOARD USER MANUAL

PM2352 FREEDM™-32P672

DEVELOPMENT KIT BOARD USER MANUAL PMC-2001840

ISSUE 1

DEVELOPMENT KIT BOARD USER MANUAL

| <u> </u> | 1                |                                                                                                                                                                               |                                                                                                                                                       |

|----------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |                  | A3 shorted to pins<br>B0, B1, B2 and B3<br>respectively                                                                                                                       |                                                                                                                                                       |

| P1       | TFPB[3:0]        | Pins A0, A1, A2 and<br>A3 shorted to pins<br>B0, B1, B2 and B3<br>respectively                                                                                                | TFPB[3:0] grounded                                                                                                                                    |

| P9       | RFP8B &<br>TFP8B | Pins in column A<br>shorted to pins in<br>column B<br>respectively                                                                                                            | RFP8B and TFP8B grounded                                                                                                                              |

| P12      | RCLK[15:0]       | Pins Ay shorted to<br>pins By<br>respectively, where<br>y = link to be<br>operated at DS3,<br>T1 or E1. The pins<br>Bz shorted to pins<br>Cz where z = link to<br>be disabled | DS3 provision to RCLK[2:0]<br>inputs of FREEDM <sup>™</sup> -32P672.<br>T1/E1 clocks connected to<br>selective links for Mixed<br>DS3/T1/E1 operation |

| P11      | RCLK[31:16]      | Pins Ay shorted to<br>pins By<br>respectively, where<br>y = link to be<br>operated at T1 or<br>E1. The pins Bz<br>shorted to pins Cz<br>where z = link to be<br>disabled      | Selected Links enabled for<br>T1/E1 operation (Mixed mode)                                                                                            |

| P13      | TCLK[15:0]       | Pins Ay shorted to<br>pins By<br>respectively, where<br>y = link to be<br>operated at DS3,<br>T1 or E1. The pins<br>Bz shorted to pins<br>Cz where z = link to<br>be disabled | DS3 provision to TCLK[2:0]<br>inputs of FREEDM <sup>™</sup> -32P672.<br>T1/E1 clocks connected to<br>selective links for Mixed<br>DS3/T1/E1 operation |

| P14      | TCLK[31:16]      | Pins Ay shorted to<br>pins By<br>respectively, where<br>y = link to be<br>operated at T1 or<br>E1. The pins Bz                                                                | Selected Links enabled for<br>T1/E1 operation (Mixed mode)                                                                                            |

PM2352 FREEDM™-32P672

DEVELOPMENT KIT BOARD USER MANUAL PMC-2001840

ISSUE 1

DEVELOPMENT KIT BOARD USER MANUAL

| i   |                 |                                                                                                                                                                                                   | ı                                                                                      |

|-----|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

|     |                 | shorted to pins Cz<br>where z = link to be<br>disabled                                                                                                                                            |                                                                                        |

| P7  | RCL52[2:0]      | Pins A-Ry shorted<br>to pins B-Ry,<br>respectively, where<br>y [y = 0,1  or  2] is<br>the link to be<br>operated at DS3.<br>Pins B-Rz shorted<br>to C-Rz where $z =$<br>links not used for<br>DS3 | DS3 selection for RCLK[2:0]<br>(One of the links 0, 1 or 2 is<br>operated at DS3 rate) |

| P7  | TCL52[2:0]      | Pins A-Ty shorted<br>to pins B-Ty,<br>respectively, where<br>y [y = 0,1 or 2] is<br>the link to be<br>operated at DS3.<br>Pins B-Tz shorted<br>to C-Tz where $z =$<br>links not used for<br>DS3   | DS3 selection for TCLK[2:0]<br>(One of the links 0, 1 or 2 is<br>operated at DS3 rate) |

| P15 | TD RD[15:2]     | Pins Ay shorted to<br>pins By<br>respectively, where<br>y = link to be<br>operated at<br>DS3/T1/E1                                                                                                | Loopback on selected links                                                             |

| P10 | TD<br>RD[31:16] | Pins Ay shorted to<br>pins By<br>respectively, where<br>y = link to be<br>operated at T1/E1                                                                                                       | Loopback on selected links                                                             |

| P2  | TD RD[1:0]      | TDy shorted to RDy<br>respectively, where<br>y = link to be<br>operated at<br>DS3/T1/E1                                                                                                           | Loopback on selected links                                                             |

Note 1: All unused RCLK and TCLK should be grounded, by placing shorting jumpers over pins of columns B and C, of the unused links. Shorting jumpers need not be placed over unused receive/transmit links.

DEVELOPMENT KIT BOARD USER

ISSUE 1